Speeding Up Your FPGA/ASIC Memory Interface (GCI)

Wednesday March 11, 2020By Mark Baumann Director, Product Definition & Applications, MoSys, Inc.

As a vendor that supports memory-based products, MoSys is very often informed about the problems and shortcomings associated with memory. Some of these are density and cycle time related but quite often the issue is the access speed and bandwidth both which are very often limited by the traditional wide parallel Address, Data bus structures used with traditional memories.

When MoSys initially began defining the Bandwidth Engine products, it was important to build in both an interface that can support future speed and maintain the high reliability that the traditional parallel bus structures provided.

To address the issue of speed, both today and in the future, it is believed that SerDes addresses this issue. Common speeds of 10Gbps up to 28Gbps are readily available on FPGAs and soon speeds of up to 112Gbps will be commonly available. This suggests that silicon manufactures and developers see a benefit in the roadmap of SerDes technology. With this understanding, MoSys wanted to take advantage of this as well.

The next issue to be addressed is the overhead associated with Serial protocols. Most serial protocols are designed with the idea that large packets transfers are the data that will be transferred. When the goal is to simply support a memory access, you only need to transfer small 1 to 8-word packets of data. To support this requirement MoSys developed GCI (Giga Chip Interface) a high efficiency, light weight (small number of gates, 20K to 40K FPGA LUTs), highly reliable, open standard that can perform all the tasks needed for a controlled point-to-point memory transactions.

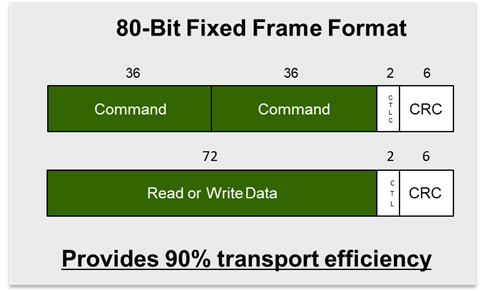

The previous figure illustrates the format of transactions over the GCI bus. The packet sent across the GCI bus is formatted into 80 bit frames with 8 bit of the 80 being dedicated to CRC (insuring that the data gets across the bus cleanly and two control or flag bits that are used in the rare occurrence that an error happens and there is a need to back-up and re-transmit data that was incorrectly received. This ‘handshake’ mechanism is instrumented in both directions and can recover errors that happen in either direction.

It has been MoSys’ experience that due to signaling being point-to-point and in most cases on the same PCB (although it is possible if a maximum of -12db trace loss is maintained, a connector crossing is possible) our data has illustrated a BER of in the range of 10 -18. This equates to an error every few years of operation.

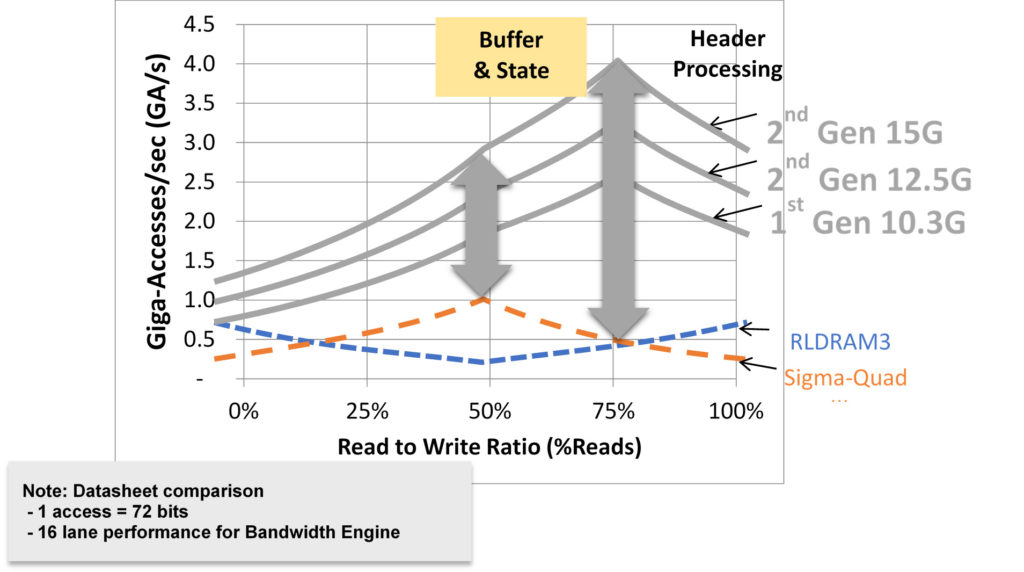

If we again review the approach that has been taken on the MoSys accelerator engine family of products, SerDes was used to provide a widely supported standard interface scheme with a roadmap for future growth in transaction speeds. This also addresses the issues of protocol and overhead when dealing with small transactions (like a memory access). In this case, the GCI protocol is 90% transport efficient for single word transactions. It can support bursts of up to 8 words and has successfully run on all versions the major FPGA manufacturers for the last eight years. Transactions between the MoSys Accelerator Engines (BE-2 and BE-3) have run at full SerDes rate allowing up to 2.5B transactions per Sec when talking with the BE-2 device and up to 5B transactions per second when interfacing with the BE-3 device.

This has proven to be a robust method of providing a future for Memory interfaces that do not require residing on a common substrate with the Host device or that need to undertake any exotic PCB or design material changes. It also allows for a clean highly reliable interface with the ability to transact between 2 and 5X that of other high throughput memory devices.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.