Put Your Development Efforts on Auto Pilot with MoSys RTL

Thursday February 13, 2020

By Mark Baumann,

Director of Product Development and Applications

MoSys, Inc.

Imagine being able to forgo development efforts for your next FPGA-based application. Imagine not having to manage schedules and budgets, setbacks and all the hassles associated with development efforts.

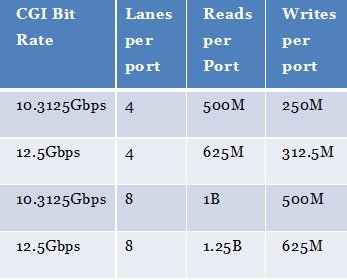

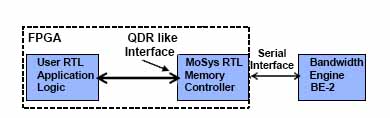

Welcome to MoSys RTL technology. MoSys has an FPGA RTL Memory Controller that interfaces with the MoSys Bandwidth Engine. This controller is between the User Application logic and the BE device and it handles all the logic for the Serial GigaChip Interface (GCI) between the FPGA and the BE virtually eliminating the need for designers to do costly and time-consuming development work. The RTL supplied by MoSys controls the GCI serial Protocol, handles issues of timing and protocol at the interface to the BE-2 and configures Memory to x8, x16, x32, etc. Utilizing a MoSys serial High-Speed GCI interface, it supports 4, 8 or 16 lanes of SerDes.

The signal interface at the User Application provides Bandwidth Engine Users a simple SRAM memory read/write operations with burst capability. This simple interface shields the users from the Bandwidth Engine commands and the scheduling logic for Bandwidth Engine memory partition timing. The Memory Controller RTL is designed to simplify and make transparent the User Application Interface of the FPGA to the Bandwidth Engine Memory. This, in turn, uses the serial16 lanes of SerDes and implements the GCI protocol.

Key features of the RTL include memory interface to User Application is User Defined. Typical I/Fs are 16, 32, 36, 64 and 72 bit and inter-operability with all FPGA vendors. The RTL control manages the address translation for the different word width to the BE memory.

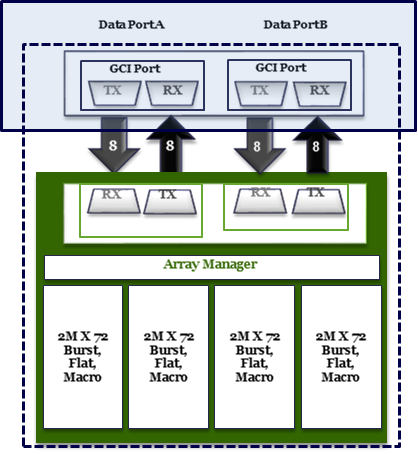

MoSys BE-2 has 576 Mb of storage and is organized as 4 partitions of 2M x 72 as shown below. The BE3 has 1Gb of storage is not shown.

Cannot get any simpler than this!

Makes the Bandwidth Engine:

- RTL presents an interface which is equivalent to a QDR parallel memory interface

- Equal or faster performance

- User defined word width

- With either 4x the memory of a QDR (BE2’s 576 Mb of memory)

- Or, with 8x the memory of a QDR (BE3’s 1Gb of memory)

More memory generally results in higher performance!

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for our newsletter. Finally, please follow us on social media so we can keep in touch.