Predicting the Future of Tech Trends

Monday January 20, 2020By Michael Miller

Chief Technology Officer, MoSys, Inc.

When it comes to making predictions in the fast moving and ever-changing world of high tech, you have to be careful, prognostication can be like looking through binoculars while trying to walk down a tightrope. The future seems so clear, but we miss and trip over what is right in front of us. So, with that in mind, in 2019 I saw 5G finally show up on my iPhone screen. That says a lot about the service finally breathing life. Since the 5G signal has finally made its debut, opportunities may start to become more viable because the reality of it is more certain.

Carriers have talked about 5G edge computing as Just a Bunch Of (homogeneous) Servers (JBOS) in a rack at the edge of the network. While this is flexible place to start from, it will probably be hard to live up to expectations. Space and power is limited at the edge. And while CPUs are flexible, they burn a lot of power when they do things they were not optimized for. This will cause its own bottleneck.

In 2020 operators will be starting to seriously look at what types of heterogenous computing makes sense in the edge as applications that take advantage of edge computing start to immerge. 2020 could be the year because the opportunity to take advantage of it is finally here.

But there is a further complication when it comes to rolling out heterogeneous solutions of CPUs plus GPUs or FPGA accelerators. What happens when some edge compute centers have accelerators and other do not? Software designers tend to code to the lowest common denominator. So, designers may not take advantage of accelerators until all installations have the same hardware. To solve this conundrum, virtualizing the accelerator function and providing implementations that span from software only to fully hardware using high speed SRAM can provide environment where the developer can rely on every edge compute center having the function.

At MoSys, we recently announced a family of Accelerator Engines that enable (embedded) acceleration or deployment of a function (such as packet filtering, packet forwarding and data analytics) that our customer is performing. At the same time, we offer an alternative or accelerated way of implementation. MoSys Accelerator Engines address the memory access rate of systems that require true random access to data.

Virtual Accelerator Engine (VAE)

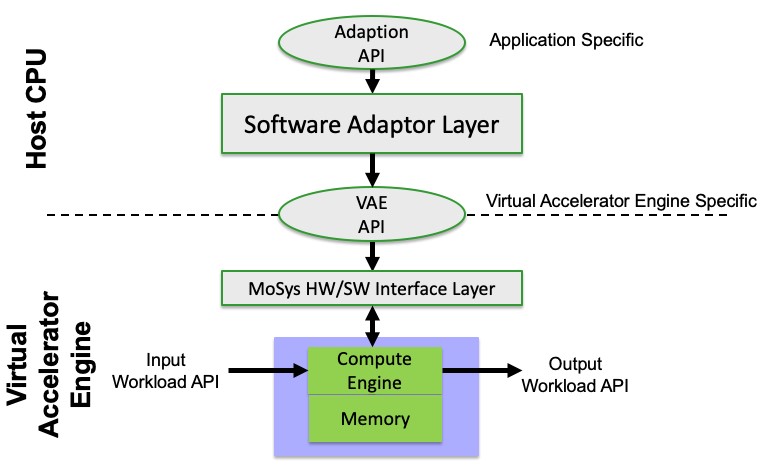

The market continues to migrate to software-defined environments, most notably software-defined networks (SDN). This means that performance scaling has become key to remaining competitive while there remains a need to address the growing requirements being placed on the network. Software now must be transferrable across multiple hardware environments in order to be both cost-effective and provide the required flexibility to meet changing performance demands.

This flexibility has led architects and designers to:

- Require a hardware agnostic solution that can run over CPUs, FPGAs and other hardware platforms.

- Seek scalable solutions that can meet their current performance needs, as well as provide a path to new products to meet new and increasing market demands.

- Look for a technology that is both cost-effective and provides the required flexibility to meet changing performance demands.

- Count on products that are easy to use and do not require learning new software.

- Expect innovation that allows users to preserve and re-use software assets.

- Adaption Layer software

- Scalable platform performance

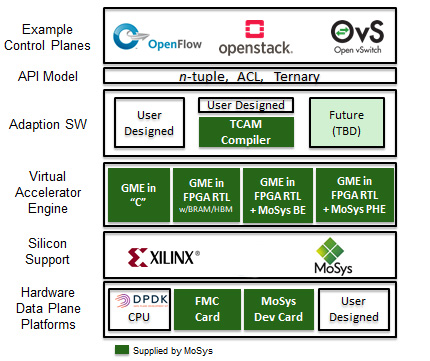

Following that, we rolled out the first products in its Software Acceleration Product Line – our new Packet Classification Platform that will make use of MoSys’ innovative virtual accelerator, the Graph Memory Engine (GME), for performing embedded search and classification of packet headers as an alternative to TCAM functions. The platform will include the GME and software that compiles TCAM images into graphs for GME processing using a common API for scalability. The GME will be provided as a family of implementations ranging from a pure software version for maximum flexibility and capacity, RTL for use in a Xilinx FPGA for hardware performance, and a maximum performance RTL solution connected to a MoSys Programmable HyperSpeed Engine (PHE) with its 32 embedded RISC cores. The initial FPGA versions of the GME are compatible with Xilinx UltraScale+ and utilize a common RTL interface to facilitate platform portability.

We have been working with Xilinx and in our press release, Farhad Shafai, vice president, communications markets, Xilinx, said, “We are delighted to see MoSys expanding its product strategy in this direction. Our industry-leading FPGAs already have proven experience interfacing with MoSys’ Bandwidth Engine serial-memory devices to accelerate networking and security applications. We look forward to collaborating with MoSys on its new platform to enable customers even higher, more scalable performance and flexibility using our advanced adaptable solutions.”

We expect to roll out new platforms over the next few quarters to address other markets. Target applications include acceleration cards, 5G edge compute, aerospace and defense, advanced video, high-performance computing and other data-driven applications.

Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help! Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for alerts and get all the news. Finally, please follow us on social media.