Packet Classification Apps Just Got a Whole Lot Easier to Manage: MoSys’s New Graph Memory Engine™ Running on Xilinx UltraScale+ with TCAM Compiler

Wednesday January 15, 2020By Gus Lignos

Vice President Sales, MoSys

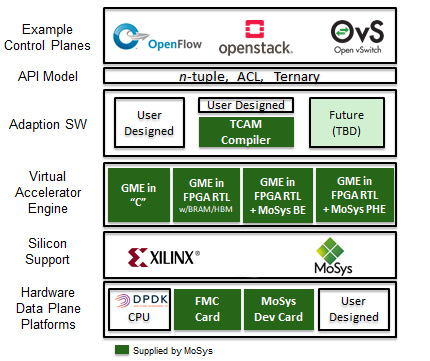

Yesterday MoSys announced the first products in its Software Acceleration Product Line – our new Packet Classification Platform that will make use of MoSys’ innovative virtual accelerator, the Graph Memory Engine (GME), for performing embedded search and classification of packet headers as an alternative to TCAM functions. The platform will include the GME and software that compiles TCAM images into graphs for GME processing using a common API for scalability. The GME will be provided as a family of implementations ranging from a pure software version for maximum flexibility and capacity, RTL for use in a Xilinx FPGA for hardware performance, and a maximum performance RTL solution connected to a MoSys Programmable HyperSpeed Engine (PHE) with its 32 embedded RISC cores. The initial FPGA versions of the GME are compatible with Xilinx UltraScale+ and utilize a common RTL interface to facilitate platform portability.

Packet classification apps are about to get a whole lot easier because the search performance on an UltraScale+ FPGA with MoSys PHE can result in up to 100x performance over software solutions running on host CPUs with DRAM, which are bottlenecked by random accesses of memory. The PHE version provides enough performance to support two 100G ethernet ports. In short, we just made our trademark acceleration available to a wider set of environments while enabling software designers to make use of hardware performance without developing firmware or RTL. This same approach can be applied to a wide variety of advanced embedded applications including key value pair databases, networking search functions, machine learning, computation and algorithm acceleration, all of which can run on different hardware platforms.

We have been working with Xilinx and in our press release, Farhad Shafai, vice president, communications markets, Xilinx, said, “We are delighted to see MoSys expanding its product strategy in this direction. Our industry-leading FPGAs already have proven experience interfacing with MoSys’ Bandwidth Engine serial-memory devices to accelerate networking and security applications. We look forward to collaborating with MoSys on its new platform to enable customers even higher, more scalable performance and flexibility using our advanced adaptable solutions.”

At a recent series of Xilinx

Developer Forums in both San Jose California and Europe, MoSys successfully

demonstrated its packet classification and layer 2 forwarding capability

targeted at FPGA-based SmartNIC, router, switching, security and cloud

applications. The interactive demonstration featured a TCAM compiler,

classifier and a Layer 2 forwarding database running on a MoSys PHE connected

to a Xilinx VU9P UltraScale+ FPGA on a PCIe card plugged into a standard server

box.

We expect to roll out new platforms over the next few quarters to address other markets. Target applications include acceleration cards, 5G edge compute, aerospace and defense, advanced video, high-performance computing and other data-driven applications.

Links:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for our newsletter. Finally, please follow us on social media so we can keep in touch.