FPGA and Memory Latency

Monday February 24, 2020By Mark Baumann

Director, Product Definition & Applications

MoSys, Inc.

One of the significant issues that MoSys has faced since the inception of the Bandwidth Engine products has been the challenge of developing a Memory product that utilized SerDes as its I/O structure.

Conventional wisdom states that for memory, the “standard” has been to employ a wide parallel bus structure utilizing LVCMOS signaling levels. This is, and has been, the tried and true structure that made up a memory. The issues that MoSys wanted to address is that while this has been a reliable method, we realized that if we were to attain even higher I/O speeds, the effort would require that the buses change to a SerDes-type structure.

It is our belief that the ability to stay with the parallel buses of LVCMOS seems to be approaching its End of Life. At least as far as a PCB level of interconnect is concerned. There are however, new die level interconnect using “Chiplets” which in many cases would require a re-design of the I/Os of a device to take advantage of the higher speed and lower signal swings that can accompany a chip to chip connection. If, however, the goal is to maintain the flexibility of PCB design, the next viable interconnect technology points to SerDes.

The two issues that are faced when utilizing SerDes are:

- What protocol to use and

- What is the impact on latency by supporting the protocol overhead and translating to a serial stream of bits vs. a broad, wide parallel bus?

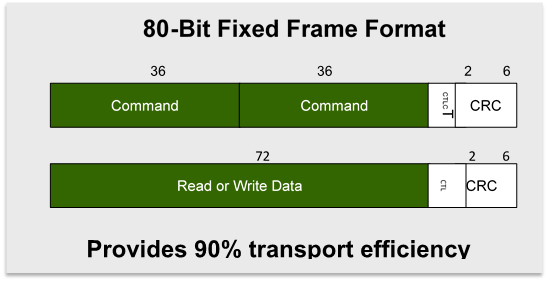

In addressing issue, a) MoSys has developed a very light weight high efficiency and reliable SerDes protocol called GigaChip Interface or GCI for short. It is an open specification and free to use, to support the needs of a memory interface that only needs to transfer words rather than large packets of data.

GCI

- High Performance GigaChip Interface

- Small logic footprint and lower system cost than other serial protocols

- Only uses features needed for point-to-point communication of fixed-size frames over short distances

- Built-in replay mechanism for error recovery

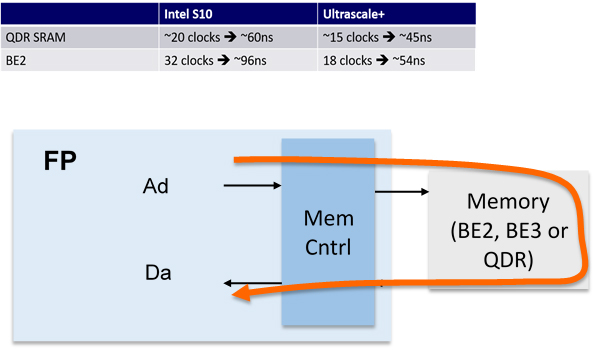

The second issue, b) relates to the impact on latency when changing the interface from a parallel structure to a serial structure. What I wish to do is point out that there are at least two ways of defining this. On a device basis it is true that the parallel structure device has a benefit over Serial. This can be seen by the specifications of a QDR SRAM which can have a read latency in the 2 or 3 ns range and a BE-2 is 16 ns. It looks on its surface that QDR will win.

But I would then suggest that looking at the latency in a system design (in this case FPGA-based) will lead to a different conclusion. In the case, that the latency is defined as the time from the controller initiating an access to the memory until the read reply is received back to the requesting host, the latency now shows a much smaller percent difference.

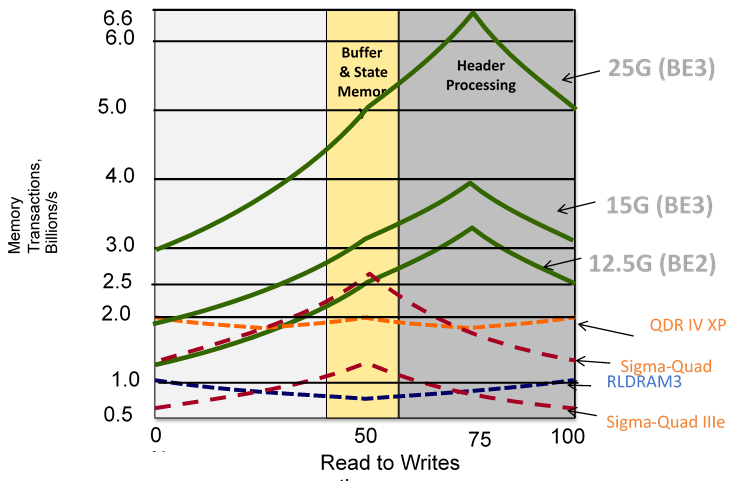

If the real measure of importance in a system is not an individual READ access but actual patterns of Reads and Writes, then a measure of throughput or bandwidth can be an even more critical parameter. When looking at a systems access pattern as percentage of Read vs. Writes the following chart emerges:

When analyzing the memory performance as it will truly be used in a system, this analysis illustrates how some of the individual device parameters can become less of a driving factor vs the performance that can be achieved when in actual use in a system.

It can be seen when reviewing both the impact on the system of protocols and system bandwidth that when utilizing a SerDes on the interface to a memory can be beneficial vs. a hinderance. In future discussions, we will look at issues such as routing, power and density that can also be improved by the use of a SerDes based-memory solution.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.