Forward Looking from MoSys in 2021

Tuesday January 5, 2021By Mark Baumann

Director, Product Definition & Applications

MoSys, Inc.

There is a tendency at this time of year to either look back at previous accomplishments or look forward to the plans for 2021.

MoSys has a significant number of accomplishments to reflect on for 2020, such as development and release of a new IC product QPR (Quad Partition Rate) which directly addresses the need for denser and faster SRAM devices and the development and delivery of the new IP offering, called the Graph Memory Engine (GME) which is the focus of the technology development at MoSys for the next few years.

The basis of the MoSys Virtual Accelerator Engine (VAE) family is the GME. What the GME has allowed MoSys to do is define and design a platform technology that presents a common API (to support both a consistent interface and portability of software and RTL interface) when utilizing a GME Packet classifier across a variety of platforms and performance goals. The MoSys GME has, at it’s core, a concept where systems are designed to address a wide variety of applications and performance goals. In reviewing these systems, a common function of classification or searching was identified. The goal was then to identify an interface or API that could be common across a variety of these systems. This is the basis of the VAE family from MoSys. The initial offering from MoSys is a Packet Classifier which is commonly utilized in networking systems. The most common applications are Longest Prefix Match (LPM) and Access Control Lists (ACL).

It may be realized that the system that each may be placed could be switches vs. routers, at their core the function being executed is a matching of a “key” to the data resident in a table. Hence the definition of the GME is to take a piece of data or Key and compare it to the data that is resident in a table. This resolves the base function to walking through a table structure (small or large) to resolve what the system needs to do as far as routing or handling the packet or data it has just received.

What will be different in each case is the size of the tables, the number of tables, are wildcard bit or fields going to be part of the search, the size of the incoming “key” data that needs to be used in the search and all of these factors are used in building the graph or memory image that is stored as an image to be searched.

In summary, the GME function is one that is consistent and common across many systems and applications. What is different is the “Type” of search (exact match, wildcard match or a combination of both) that will drive how a graph is defined and built, (when reviewing this IP is becomes clear that speed of execution will be linked to the speed of memory accesses by the GME IP) as well as defining how the search will take place in the GME. In the initial instantiations for the VAE MoSys has developed a Packet classifier.

The GME is available as:

- Software only (C Code that can be compiled to run on a CPU)

- RTL only (available as pure RTL to be used in an ASIC, or as available code to be used in either an Intel or Xilinx FPGA)

- RTL with an acceleration of using a MoSys BE-2 or BE-3 Memory device (allowing for larger tables than a FPGA only option)

- RTL and assembly code that resides on an MoSys PHE (Programmable Hyper-Speed Engine) which is a 1Gb memory device with 32 RISC cores on die which allows up to 1.5Tbps of memory access.

- RTL on an FPGA with a final stage lookup or search table being in DDR or HBM to allow for very large tables or possibly even to allow for a block of data to be returned as a result of the search

As mentioned earlier the interface or API to interface with all the GME options is common and allows for a “tuning” of performance by selecting which version fits best into the system being designed.

I realize this has been a lengthy summary of what MoSys has already developed, but I wanted this to be a baseline understanding of the core IP (the GME) that MoSys has developed. What MoSys believes is the future direction will be to extend the GME IP into additional markets. This will require significant development across the offerings:

- New versions of GME that address Security Markets with Functions like Allow/Deny Lists, DDoS prevention

- Load Balancing (Application Delivery Controllers)

- 5G UPF (User Plane Function)

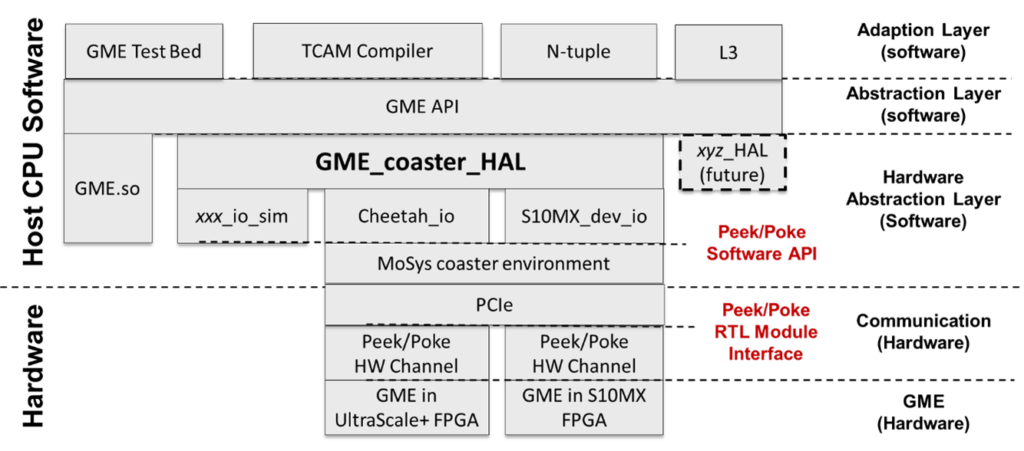

With each new functional market that will be supported, there will be development of graph compilers to build the graphs for the appropriate data set (See the figure below to see how the IP fits in a system).

HAL – hardware Adaptation Layers that interface the data application set to the GME

RTL to address the new search requirements of each function to the memory available for the tables, which needs to be adapted to different platforms (such as Intel and/or Xilinx).

The development efforts at MoSys will be focused on expanding the reach of this unique IP and adapting it to support applications and systems in addition to the present network packet classification area that it currently supports.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.