Two Roads Diverge: How To Accelerate Your Future Part I: Hardware

Tuesday May 12, 2020By Julie DiBene

Director, Marketing Communications

MoSys, Inc.

As we all continue to shelter in place and work from home, I find myself with a bit more time on my hands and feeling reflective. In the process, I happen to unearth a poem I have always loved by Robert Frost called The Road Not Taken. I find that poem applicable to so many situations, including, curiously, making technical choices. The poem begins:

Two roads diverged in a yellow wood,

And sorry I could not travel both

And be one traveler, long I stood

And looked down one as far as I could

To where it bent in the undergrowth;

Seems like making decisions are a lot like that, you cannot always choose both options and you therefore have to make a decision. At MoSys, we’ve made it easy to choose between those two classic tech options for accelerating your applications; hardware and software.

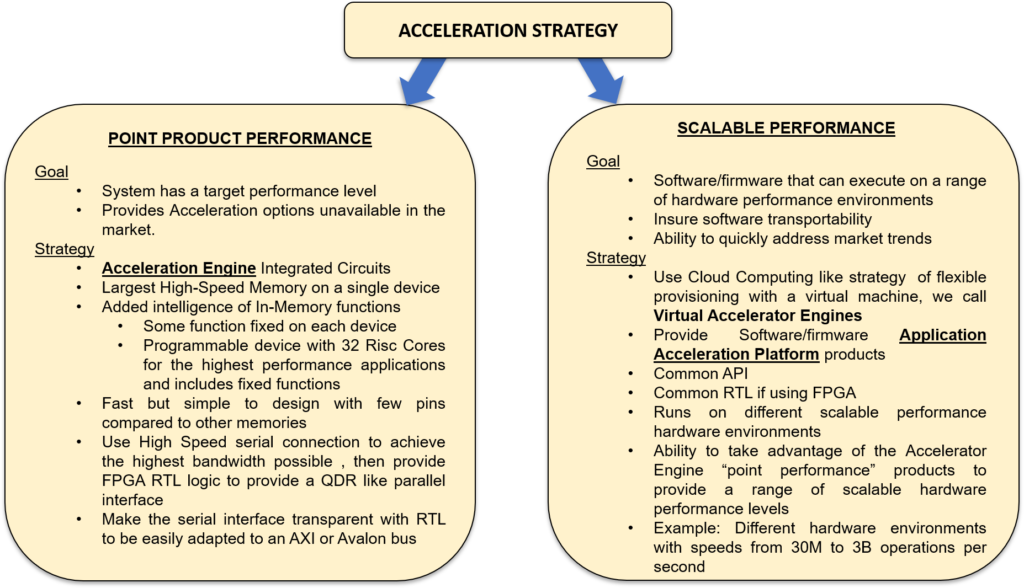

When MoSys decided that it would use the 1-T memory and define an Acceleration Product strategy, the goal was to increase performance of ASIC and FPGA applications in a way no other products on the market had.

As we know, high-speed systems today use a FPGA (Field Programmable Gate Array). MoSys acceleration technology can be leveraged to accelerate these applications in such areas as networking, video, test & measurement, AI, Machine Learning, etc. The beauty of our solutions is that they can accelerate current systems while also providing a path to higher performance and more flexible applications. MoSys acceleration alternatives enable customers to eliminate those system data bottlenecks associated with limited memory access. In addition, when using the MoSys In-Memory intelligence capability, the solutions also provide additional acceleration by offloading common, time draining functions from the CPU or FPGA.

So, knowing the benefits of this technology, the decision now becomes hardware or software? In Part I of this blog, we will cover hardware impacts first.

If your goal is to design or upgrade a system with a targeted performance level with acceleration not available anywhere else, consider MoSys’s integrated circuits. Here you can find the industry’s largest high-speed memory on a single device featuring a single circuit with 567Mb to 1 Gb and tRC of 3.2ns. This option is a great solution for replacement or to increase the capacity of a QDR type read/write memory interface. With the added benefit that the current RTL interface is most likely easily adaptable to the interface logic needed to interface with a MoSys device.

As an additional incentive the MoSys devices offer is added intelligence of In-Memory functions along with optional add-in accelerator features that are not available in a standard high-speed memory, such as QDR. These are OPTIONAL features that are available, if your application can benefit from their use. These optional features include BURST which is ideal for high-speed data movement used in sequential read or writes and an RMW function which features multiple ALUs in the memory for Read/Modify/Write operation need for compute and decision operations.

An even higher performance option includes a Programmable device, for HyperSpeed acceleration which includes the addition of 32 powerful RISC cores on the die with 1Gb of memory, which makes available to a system designer or architect options embedded user-defined functions.

We also understand that a major consideration in designing in a new IC is complexity of PCB design, logical interface and any driver changes that need to be developed and tested. The solution(s) from MoSys are developed as high performance but simple to design. MoSys can provide both controller and Interface RTL to be used in your system or if preferred, some sample code is available which would allow you to uniquely develop your own custom logic.

When considering the PCB design, a MoSys device requires far fewer pins compared to other memory chips. Reducing pin count to as low as possible is efforted by using SerDes interface between the device and the FPGA. This results in a designed that can use as little as 32-pins or, if lower performance is permitted, just 16 pins. Using the high-speed serial connection to achieve the highest bandwidth possible, the FPGA RTL logic now provides a QDR like performance with the highest efficiency, lowest pin count serial protocol on the market.

In Part 2 of this blog, we will delve into the MoSys software options that can acceleration your most demanding applications.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.