Cyber Security in Turbulent Times Part 2 of 2

Thursday April 30, 2020By Julie DiBene

Director, Marketing Communications

MoSys, Inc.

In Part 1 of this blog, we discussed the challenges of cyber security and how the growing volume of network traffic needing to be queried is increasing over time. We covered anomaly detection in cyber network traffic, and how keeping statistics on these anomalies is an important function to support detection, which in turn requires using a high random-access rate memory, performing millions of memory reads in order to develop thousands of histograms related to the traffic profiles.

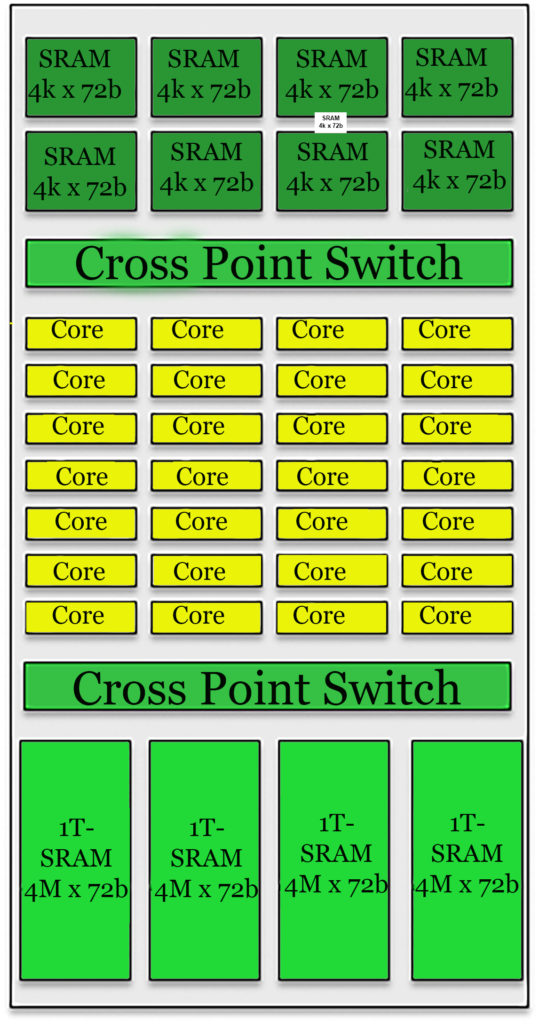

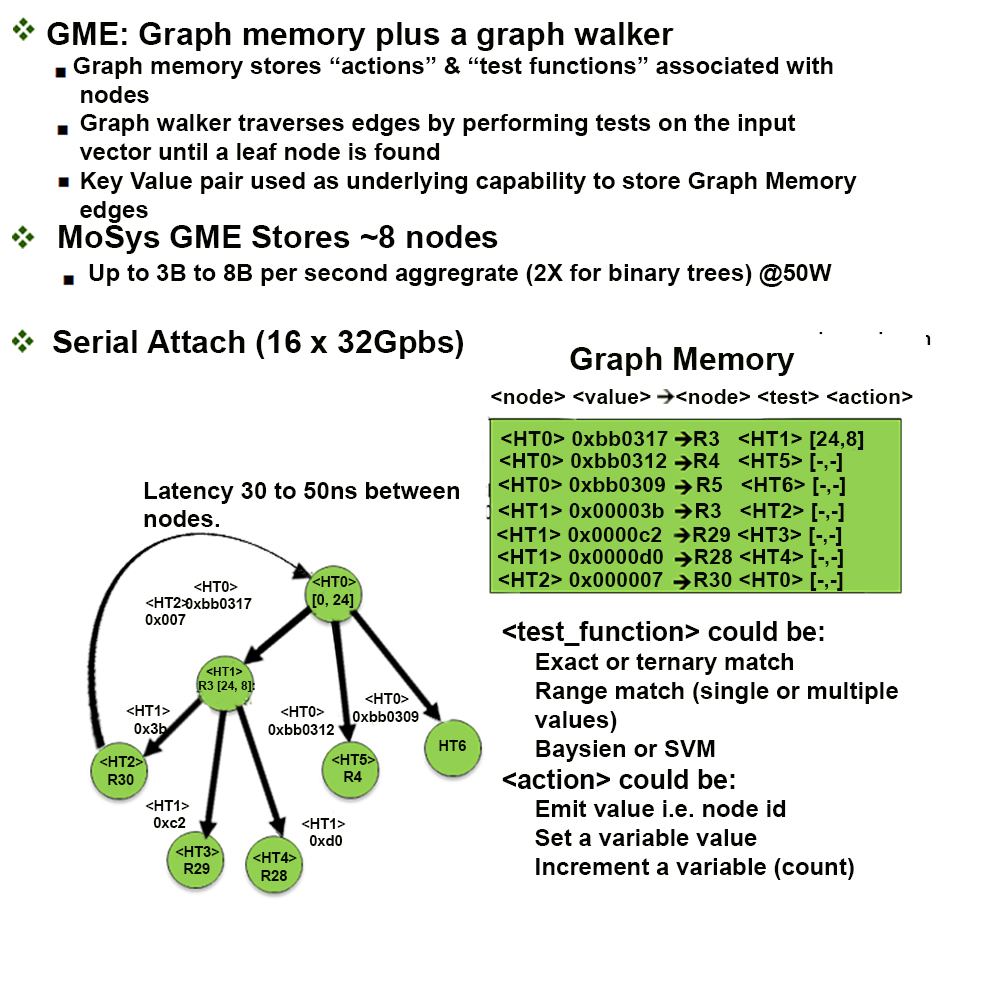

The MoSys (Graph Memory Engine) GME utilizes a proprietary high random-access rate memory with in-memory compute functionality which is ideal for searching and classifying applications — required in systems that support applications such as genomics, bioinformatics, and network security. A version of the GME has been ported onto a MoSys monolithic IC. The Programmable Hyper-Speed Engine (PHE) has 1 Gb of internal memory, 32 RISC processing cores, and supports an on die bandwidth of ~1.5 Tb/s.

The 1T SRAM is exclusively provided by MoSys and offers many of the features of traditional 6T SRAM but with a much smaller unit cell, allowing for high memory density and lower latency than is available with DRAM or RLDRAM.

Figure 1 illustrates a portion of the architecture of the PHE, which includes RISC cores, with multiple levels of RAM to support the function of the cores. Much of the additional speed-up occurs from the ability to have the RISC cores, being on the same die as the 1Gb of high-speed memory. The two are connected through a cross-point switch.

Unlike traditional classification functions running on a processor, the GME is not limited by DRAM access rates and latency; instead it leverages the PHE’s ability to achieve very high random-access rates to the on die 1Gb of high-speed memory. The architecture of the PHE enables graphs to be processed at 3 to 6 Billion nodes per second with an average latency of ~30-50 ns per node.

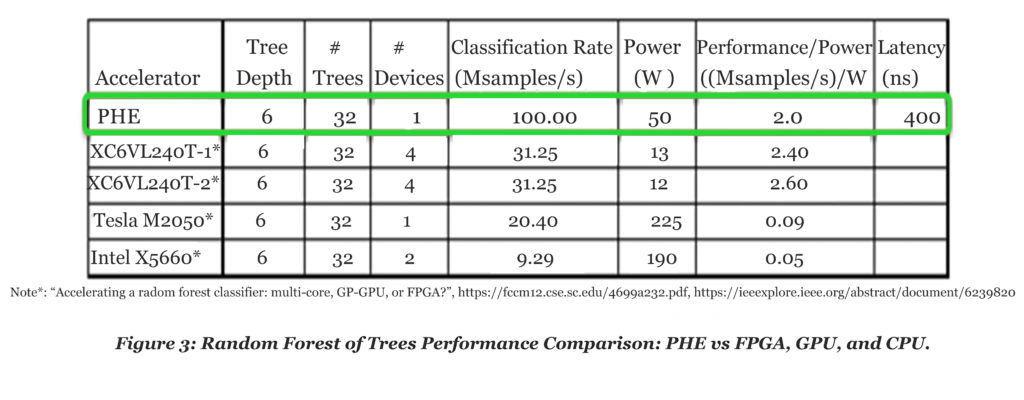

Figure 2 illustrates an example graph structure, which can be implemented to support functions like network security and genomics. Performance of algorithms used in hierarchical data structures, like random forest of trees, decision trees, and graphs are directly dependent on the number and depth of the graphs/trees required to perform a classification. In addition, the speed of traversing the graph is directly linked to the memory access rate of the processor. Figure 3 offers a Random Forest of Trees Performance Comparison of PHE vs. FPGA, GPU and CPU.

Figure 2. Demonstration of GME used for Graph Walking.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.