Serial Provides Flexible Interface for Chiplets Interconnect

Thursday February 6, 2020By Michael Miller

Chief Technology Officer

MoSys, Inc.

Chiplets are a hot topic in the industry. Similar to the multi-chip module concept that has been around for 20 years, the idea is re-usable functional circuit blocks combined to deliver a solution with the benefits of lower cost, smaller size, and faster design time. The key difference today is that they can be connected into extremely dense systems using interposer technology or next-generation substrate technology for much higher pin density.

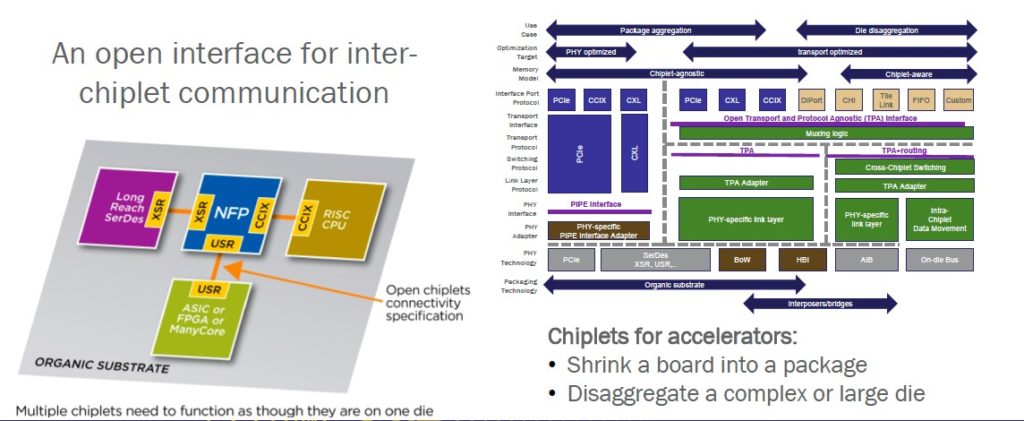

The industry is keenly interested in chiplets and government and industry bodies have been initiated to create solutions: DARPA created a program called CHIPS and an industry group called ODSA (Open Domain-Specific Architecture) which is now under the OCP (Open Compute Project) umbrella. Both are working to establish industry standards and an ecosystem for chiplets. The chiplet concept and details of connection is summarized in the ODSA diagram below:

One of the key decisions for chiplets is the interconnect or I/O. There are two basic options available – serial or parallel which is basically, narrow and fast (fewer lanes running at high data rates) or wide and slower (100s or 1000s of lanes running at slower rates).

Parallel busses such as the High Bandwidth Interconnect used in the High Bandwidth Memory (HBM) deliver high bandwidth, low latency and relatively low IO power. In general, the parallel interface will deliver the highest bandwidth and lowest latency at the lowest power. Prior to interposer technology, the parallel interface was just too wide, making chip sizes large and high bandwidth interconnect unfeasible. Interposer technology has provided a solution to this limitation by drastically increasing the pin density between chips. That being said, interposers force significant layout limitations while adding manufacturing costs and thermal challenges.

Serial connections have been used in the industry for decades and new low power chip-to-chip interfaces like USR allow for high bandwidth, low cost connectivity across standard substrate materials and placement flexibility and thermal benefit. While there are new signaling technologies like PAM4, standard NRZ signaling techniques provide the most proven low power and low latency serial connection for chiplets. The typical drawbacks brought up for any serial interface are power and latency. The power of high-speed serial interfaces are generally higher than single ended parallel connections, but all interfaces are still dominated by voltage swing (v2cf). Added latency comes from the fundamental serialization and deserialization that is required with the high-speed interfaces and from the serial protocol that is used.

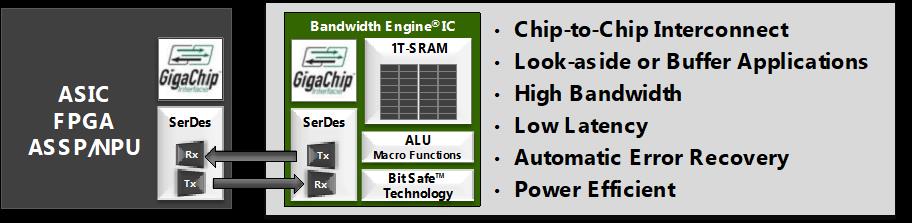

The power and latency drawbacks of serial interfaces can be minimized. As an example, MoSys products incorporate a CEI-25G SerDes where the total Tx + RX including deskew latency is under 3ns and the products also incorporate a low latency protocol (Gigachip Interface or GCI) that provides nearly an order of magnitude lower latency than other serial protocols to help minimize latency. If manufactured in die form, the Bandwidth Engine itself is a virtual chiplet.

By leveraging existing low latency serial technologies like those developed for the MoSys Bandwidth Engine family, the industry has viable serial options that will deliver higher flexibility, lower cost options using standard substrate materials while minimizing the power and latency penalties.

Resource Links:

If you are looking for more technical information or would like to discuss your design issues with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for our newsletter or request a quote from sales. Finally, please follow us on social media so we can keep in touch.