New Quazar Family of High-Speed SRAMs from Mosys Part 2 of 2

Thursday July 23, 2020By Mark Baumann

Director, Product Definition & Applications

MoSys, Inc.

In Part 2 of this new blog series, we will discuss and compare the MoSys and QDR approach to these devices.

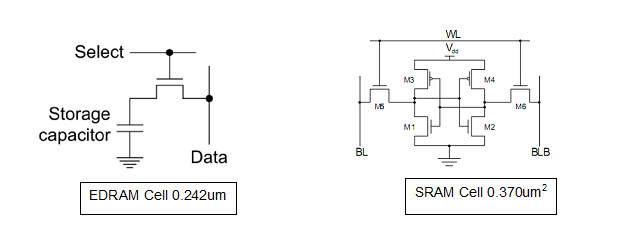

The cell design that MoSys has chosen to use in the Quazar product line uses an embedded DRAM design. Benefits include a Reduced driver size, lower power, faster speed and a solution that is approximately 53% larger than the EDRAM cell.

Due to the unique Quad Partition structure of the MSQ devices, and the fact that during each FPGA clock cycle the MSQ device will access all 4 partitions in a TDM fashion, this equates to each partition must complete the memory access in the specified Trc associated with the associated FPGA clock rate and within that clock time an access will happen in each of the 4 partitions. This results in 4 independent access in one FPGA clock cycle.

This unique partitioning and round robin access pattern allows for the flexibility and increased Bandwidth over SRAM like QDR.

The next innovation in the MoSys memory architecture is the division of the memory array into Quad Partitions. A partition in the case is either a 2M x 72 (144Mb) in the case of the MSQ220 or 4M x72 (288Mb) in the case of the MSQ230. This is equivalent to the density of the present QDR devices. Since the MoSys device has 4 partitions, it is equivalent to 4 QDR devices in one package.

In addition to the density, the bus structure allows each partition to be accessed as a fully independent memory structure or as part of a unified memory. This enables the user to access 4 independent 72-bit words, one in each of the 4 partitions, from each of the GCI ports.

Summary

The unique architecture of the MoSys Multi-Partition-Rate devices offers users SRAM like access to a next generation memory. This device offers Bandwidth, Speed, availability, with a solid roadmap to increased functionality. These devices are ideal for replacement and enhancement of present day QDR applications. MoSys does not only support the device but in addition it offers sample RTL for the controllers that have been proven functionality in most families of FPGAs. There is a white paper that expands greatly on this blog series that can be downloaded by clicking on the link in Additional Resources.

Additional Resources:

If you are looking for more technical information or need to discuss your technical challenges with an expert, we are happy to help. Email us and we will arrange to have one of our technical specialists speak with you. You can also sign up for updates. Finally, please follow us on social media so we can keep in touch.