Burst Accelerator Engine ICs

Device Features

- 1.152 Gb memory with SerDes I/O

- Accessible through as few as 4 Lanes and as many as 16

- Deterministic Latency

- Embedded In Memory Functions

- Burst 2, 4 or 8 (EMIF)

- Two Separate Access Ports

- Full Production Qualified and Available

Superior, High Speed Random Access Memory Architecture

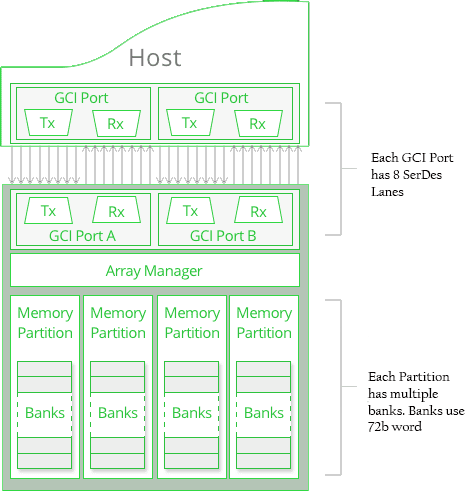

The heart of the memory IC is our advanced & parallel array of 1-T SRAM with a capacity of 1.152Gb.

- The memory is divided into 4 partitions allowing parallel (simultaneous) access. Each partition has 128 banks.

- There are two independent I/O ports per device, allowing for several memory access as well as multiple EIMFs to be executed in the same timeframe.

- Can be used as a Dual-Port memory

The tRC is 2.67 ns allowing up to 5 billion transactions per second.

Fixed In-Memory BURST Functions

The BURST Functions are focused on DATA MOVEMENT to accelerate getting data in and out of the memory faster and more efficiently by reducing the number of command cycles.

The BURST Read/Write In-Memory Functions can combine up to 8 READS and 8 WRITES into a single BURST command. This reduces the number of command cycles when moving data, nearly tripling the amount of data that can be moved in the same timeframe.

The Accelerator Engine can do several BURST Functions simultaneously, further increasing system performance.

High-Speed Serial Protocol I/O Interface

MoSys’s Accelerator Engines are designed using 16 SerDes lanes that can transmit data up to 25Gbps, with optional rates of 12.5Gbps & 15Gbps. MoSys’ GigaChip Interface (GCI) delivers full duplex, CRC protected data throughput, enabling up to 5 billion memory transaction per second on as few as 16 SerDes Lanes.

Traditional memory design requires many more interface pins (in some cases 1000s of pins), making signal routing and integrity a design challenge.

Each Accelerator Engine has 2 independent, 8 lane, I/O ports that allow simultaneous memory access operations.

The Ideal Replacement for Your Current QDR SRAM

QDR, SRAM provides speed and bandwidth, however the fact that sometimes you need multiple of them with the high signal pin count needed to get the performance needed. MoSys’s multiport, serial, single-transistor SRAM eliminate all of these issues.

One MoSys device, replaces multiple QDR SRAMs.

Easy to Design-In

- Fewer pins using serial I/O with the GigaChip Interface technology

- Clean and reliable signal integrity board layout

- Standard replacement for QDR

- Simple to understand EIMF (Embedded In-Memory Functions) to accelerate performance

- High speed random access memory, with easy to understand EIMFs, with so few signal pins

- Architected to allow for a straight-forward design-in process

Bandwidth Engine 3 – BURST Architecture

Understanding MoSys’ Advanced 1T-SRAM Technology

Parallel Array Architecture

- 16 outstanding transactions

- 6.5 Billion Transactions per Second (5B Reads & 1.5B Writes)

- 320Gbps full duplex throughput

- 2.67ns Random Cycle time (tRC)

GigaChip Interface

- 90% efficient throughput

- Up to 16 low-latency SerDes lanes (12.5Gbps, 15Gbps or 25Gbps)

Single-Cell SRAM 70x better SER

- Full ECC support

- CRC protected and self-recovering

- SEU resistant

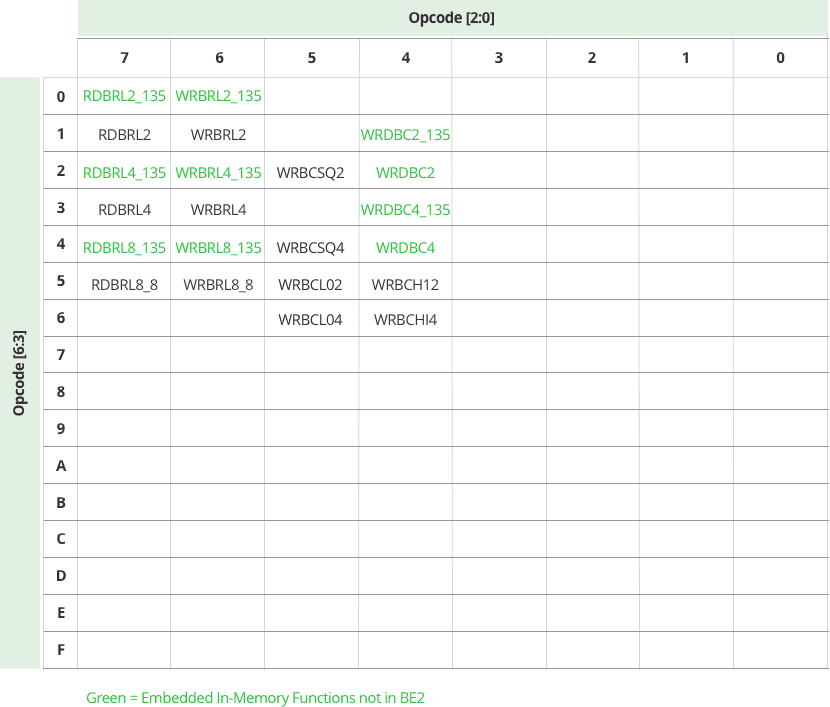

BE3-BURST Embedded In-Memory BURST Functions

BURST Fixed-Functions

Burst functions are designed to get data in and out the memory more efficiently by reducing the number of commands. Normal transmission requires one command for each transfer of data. However, by bundling eight data words to a single command, it eliminates seven unnecessary command cycles. The Burst commands enable the transmission at 2, 4 or 8 words* per command cycle.

* word = 72 bits

| SerDes Speed Grade | ||||

| 12.5Gbps | 15Gbps | 25Gbps | ||

| Width | BURST | Throughput (Gbps) | Throughput (Gbps) | |

| 16 Lanes | BL8 | 160 | 200 | 320 |

| BL4 | 144 | 180 | 288 | |

| BL2 | 120 | 150 | 240 | |

| 8 Lanes | BL8 | 80 | 100 | 160 |

| BL4 | 72 | 90 | 144 | |

| BL2 | 60 | 75 | 120 | |

| 4 Lanes | BL8 | 40 | 50 | 80 |

| BL4 | 36 | 45 | 72 | |

| BL2 | 30 | 38 | 60 | |

* Low Power Option

BE3 Embedded In-Memory BURST Function Opcode Map

* 135 b operations available for High Speed ASIC Designs